ARM通识

ARM采用32位架构

ARM约定一个Byte是8 bits,一个Halfword是16 bits (2 byte),一个Word是32 bits (4 byte)。

大部分ARM core 提供ARM 指令集(32 bit,每条指令都是4个字节),Thumb 指令集(16bit),Thumb2指令集(16 & 32bit)。

ARM的7种基本工作模式

ARM的工作模式分为普通模式、特权模式,其中特权模式又细分为六种模式。诸多模式是为了满足操作系统的安全等级需要,各种模式下可以访问的寄存器不同。

注意: 同一时刻CPU只处于其中一种模式, 程序员可以修改CPSR寄存器,实现各个模式的切换;CPU在某些情况下也会自动切换。

普通模式(Normal) (1)用户模式(User):非特权模式,大部分任务执行在这种模式。

特权模式(Privilege) (2)快速中断模式(FIQ):当一个高优先级(fast) 中断产生时将会进入这种模式。

(3)普通中断模式(IRQ):当一个低优先级(normal) 中断产生时将会进入这种模式。

(4)超级用户模式(SVC):当复位或软中断指令执行时将会进入这种模式。

(5)中止模式(Abort):当存取异常时将会进入这种模式。

(6)未定义模式(Undef):当执行未定义指令时会进入这种模式。

(7)系统模式(System):使用和User模式相同寄存器集的特权模式。

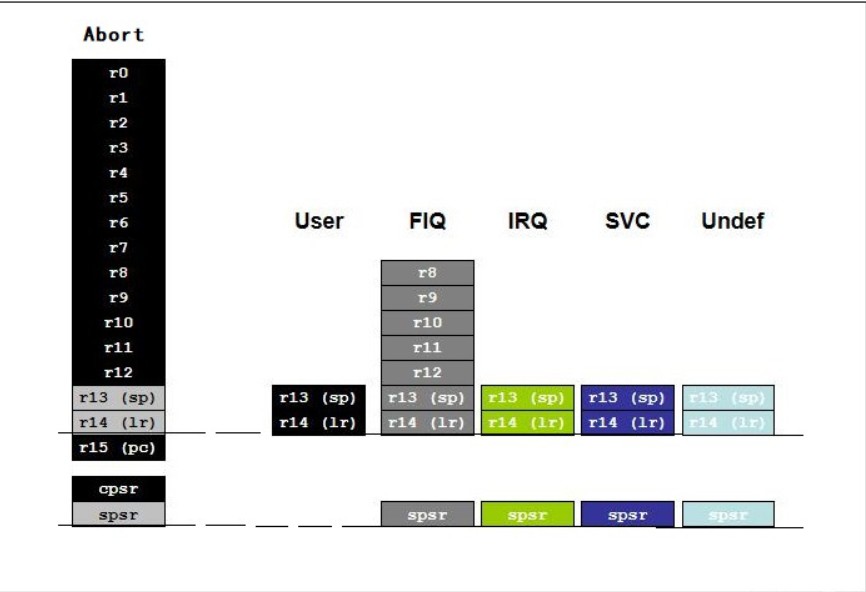

ARM的37个通用寄存器

(1)通用寄存器 通用寄存器是CPU的组成部分,CPU的很多活动都需要通用寄存器的支持和参与。

通用寄存器没有地址,通过寄存器名字来访问。

ARM一共有37个通用寄存器。

(2)特殊功能寄存器 特殊功能寄存器,属于外设硬件的组成部分。使用软件编程控制某一硬件,其实就是编程读写这个硬件的特殊功能寄存器。

注意,特殊功能寄存器有地址,通过地址来访问寄存器。

(1)影子式设计 注意,上图中除了Abort模式列出所有的寄存器外,其他模式只列出对应位置该模式下特有的寄存器,没有列出的寄存器,则说明和Abort模式共用。比如User模式下有自己的r13和r14寄存器,其他寄存器和Abort模式相同。这样算下来,ARM总共有 37 个寄存器,但最多只能同时存在18个寄存器。有些寄存器虽然名字相同,但是在当前模式是不可见的。比如在ARM中有6个名叫r13的寄存器,但在特定处理器模式下,只有一个r13是当前可见的,其他的r13必须切换到对应的模式才能看到。这种设计叫影子寄存器。

这样设计的好处是,当各种异常发生的时候,每种异常模式都可以保存一些重要的数据,异常处理程序完成之后返回异常前的程序时,不会破坏原有的寄存器或状态。

(2)重要的寄存器 这37个寄存器都是32位长度,值得重点理解的寄存器有以下几个。

- 程序控制寄存器(PC,Program Control Register)

这个寄存器存放着将要执行的指令的地址,它指向哪里,CPU就会执行哪条指令,所以程序跳转时把目标代码的地址放到PC寄存器中。注意,整个CPU只有一个PC寄存器。

- 程序状态寄存器(CPSR,Current Program Status Register)

这个寄存器用来记录CPU的当前状态。注意,整个CPU只有一个CPSR寄存器。

- 程序状态保存寄存器(SPSR,Saved Program Status Register)

用来保存CPSR的,子程序返回时将SPSR赋给CPSR。注意,整个CPU有5个SPSR寄存器。

- 链接寄存器(LR,Link Register)

这个寄存器的主要作用如下。

一是调用子程序时,用来保存子程序返回地址(子程序返回时返回到哪个地址)。当通过bl或blx指令调用子程序时,硬件会自动将子程序返回地址保存在LR寄存器中。在子程序返回时,把LR的值复制到PC即可实现子程序返回。比如可以使用mov pc,lr完成子程序返回。

二是当异常发生时,LR中保存的值等于异常发生时PC的值减4,因此在各种异常模式下可以根据LR的值返回到异常发生前的相应位置继续执行。

程序状态寄存器(CPSR)

程序状态寄存器(CPSR)在CPU中只有一个,是32bit的,记录着CPU的当前状态。

程序状态寄存器每个bit的含义如下。

(1)bit31~28是条件位

N = Negative result from ALU Z = Zero result from ALU C = ALU operation Carried out V = ALU operation oVerflowed (2)bit27是Q位

仅ARM 5TE/J架构支持,用来指示饱和状态。

(3)bit24是J位

仅ARM 5TE/J架构支持,J = 1处理器处于Jazelle状态。

(4)bit7~6是中断禁止位

I = 1 表示禁止IRQ。 F = 1 表示禁止FIQ。 (5)bit5是T位

仅ARM xT架构支持。 T = 0 表示处理器处于 ARM 状态。 T = 1 表示处理器处于 Thumb 状态。 (6)bit0~4是Mode位

这是处理器模式位。

(7)总结

CPSR中各个bit位表明了CPU的某些状态信息,这些信息非常重要,和后面学到的汇编指令息息相关(比如BLE指令中的E就和CPSR中的Z标志位有关)。

CPSR中的I、F位和开中断、关中断有关。

CPSR中的mode位(bit4~bit0共5位)决定了CPU的工作模式,在uboot代码中会使用汇编进行设置。

ARM指令集

ARM 存储器访问指令

ARM 处理器是冯诺依曼存储结构,程序空间、RAM 空间及IO 映射空间统一编址,除对对RAM 操作以外,对外围IO、程序数据的访问均要通过加载/存储指令进行。

ARM 的加载/存储指令是可以实现字、半字、无符/有符字节操作;批量加载/存储指令可实现一条指令加载/存储多个寄存器的内容,大大提高效率。

LDR 和STR 加载/存储

|

|

LDM和STM 批量加载/存储指令

|

|

SWP 寄存器和存储器交换指令

|

|

ARM 数据处理指令

数据处理指令大致可分为3 类:

(1)数据传送指令(如MOV、MVN)

(2)算术逻辑运算指令(如ADD,SUM,AND)

(3)比较指令(如CMP、TST)。

数据处理指令只能对寄存器的内容操作。

所有ARM 数据处理指令均可选择使用S 后缀,以影响状态标志。比较指令CMP、CMN、TST和TEQ不需要后缀S,它们会直接影响状态标志。

MOV 数据传送指令

|

|

MVN 数据非传送指令

|

|

加减运算指令

|

|

逻辑操作指令

|

|

比较指令

|

|

乘法指令

ARM7TDMI(-S)具有32×32 乘法指令、32×32 乘加指令、32×32结果为64 位的乘法指令。

|

|

ARM 跳转指令

两种方式可以实现程序的跳转:

(1)使用跳转指令直接跳转,跳转指令有跳转指令B,带链接的跳转指令BL ,带状态切换的跳转指令BX。

(2)直接向PC 寄存器赋值实现跳转。

|

|

ARM 协处理器指令

ARM 支持协处理器操作,协处理器的控制要通过协处理器命令实现。

|

|

ARM 杂项指令

|

|

ARM 伪指令

ARM 伪指令不是ARM 指令集中的指令,只是为了编程方便编译器定义了伪指令,使用时可以像其它ARM 指令一样使用,但在编译时这些指令将被等效的ARM 指令代替。

ARM伪指令有四条,分别为ADR 伪指令、ADRL 伪指令、LDR 伪指令和NOP 伪指令。

|

|